News Focus

제품 및 Tools

주요 시스템 및 플랫폼 디자이너들에게 최고의 생산성을 제공하는 비바도 디자인 수트 HLx 에디션 출시

주요 시스템 및 플랫폼 디자이너들에게 최고의 생산성을 제공하는 비바도 디자인 수트 HLx 에디션 출시

2015-12-02

자일링스는 올 프로그래머블 SoC, FPGA의 디자인과 재사용 가능한 플랫폼 개발에서 최고의 생산성을 제공하는 비바도(Vivado)® 디자인 수트 HLx 에디션을 출시한다고 밝혔다. 새로운 HLx 에디션에는 HL 시스템 에디션, HL 디자인 에디션과 HL WebPACK™ 에디션이 있다. 이 모든 HLx 에디션은 C/C++ 라이브러리, 비바도 IPI(IP Integrator), LogicCORE™ IP 서브시스템, 전체 비바도 구현 툴 수트 등 가장 생산적이고 최첨단인 C 및 IP 기반 디자인 플로우를 쉽게 활용할 수 있는 비바도 HLS(High-Level Synthesis)가 포함된다. 새로운 울트라패스트(UltraFast)™ High-Level 생산성 디자인 방법론 가이드와 함께 사용할 경우, 사용자는 기존 방식보다 10~15배 더 높은 생산성을 누릴 수 있으며, 이 HLx 에디션은 비바도 디자인 수트에서 무료로 업그레이드할 수 있다.

재사용 가능한 플랫폼 개발 및 프로그래밍으로 최고의 생산성

지난 3년 동안 첨단 기술을 보유한 자일링스 고객들은 현재 HLx 에디션에 포함된 C 및 IP 기반 디자인 기술 및 방법론을 개척하여 발전시켰고, 10~15배의 잠재적인 생산성을 입증해왔다. 고객들은 이 생산성을 실현하기 위해 1) C 기반 디자인 및 최적화된 재사용, 2) IP 서브시스템의 재사용, 3) 통합 자동화, 4) 가속 디자인 마무리 등 전체 또는 일부를 채택했다.

디자인 대부분이 디자인 프로세스의 최종 단계에서 소모되는 지금까지의 RTL 기반 디자인과 달리, C 및 IP 기반 디자인은 특히, 디자인 재사용이 탁월해 개발 속도가 빠르고, 보다 나은 세부 아키텍처를 위한 신속한 디자인 탐구가 가능하다. 이로써 오류가 쉽게 발생하는 C의 RTL 수동 변환을 대치하고, C 및 RTL 기반 IP를 통합하는데 드는 시간 및 오류를 덜어주며, 검증 시간을 크게 줄여 준다. 고객들은 High-Level 추상화(abstraction)를 이용해 전반적으로 더 뛰어나거나 동등한 결과 품질(성능, 전력, 활용도)을 빠르게 얻을 수 있다.

이렇게 높은 생산성 흐름을 위해 HLx 에디션은 비바도 HLS, 비바도 IPI, LogicCORE IP 서브시스템, 전체 비바도 구현 툴 수트가 포함되어 있다. 또한 자일링스와 그 얼라이언스 에코시스템은 비디오, 이미지 처리를 위한 OpenCV 및 첨단 운전자 보조 시스템(ADAS)용 머신 학습, 데이터센터 애플리케이션과 같은 시장별 맞춤형 C 라이브러리들을 지속적으로 확대하고 있다. 자일링스의 새로운 LogiCORE IP 서브시스템은 구성 능력이 매우 뛰어난 시장 맞춤형 빌딩 블록으로써, 최대 80개의 개별 IP 코어 및 소프트웨어 드라이버, 디자인 예시, 테스트 벤치 등을 통합하고 있다. 이 새로운 IP 서브시스템을 이더넷, PCIe®, 비디오 처리, 이미지 센서 처리 및 OTN 개발 등에 이용할 수 있다. 또한 IP 서브시스템은 AMBA® AXI 4 인터커넥트 프로토콜, IEEE P1735 암호화, IP-XACT와 같은 산업 표준을 바탕으로 자일링스 및 얼라이언스 회원사 IP와 상호운용성을 보장하고 통합 속도를 앞당긴다.

C 기반 IP 및 사전 패키지 IP 서브시스템은 통합 자동화를 위해 비바도 IP 통합기를 활용하여 빠르게 결합된다. 비바도 IPI의 통합 자동화는 디바이스와 플랫폼을 인식하는 인터랙티브 환경을 통해 핵심 IP 인터페이스의 인텔리전트 자동 연결과 클릭 한 번으로 IP 서브시스템 생성, 실시간 DRC, 인터페이스 변동 전달 능력과 함께 강력한 디버그 능력을 지원한다. 이 플랫폼 인식 인텔리전스는 정확한 주변장치와 드라이버, 메모리 맵으로 징크(Zynq)® SoC 및 MPSoC 프로세서 시스템을 미리 구성하여 타깃 보드를 지원할 수 있다. 디자인 팀은 이제 ARM® 프로세서 시스템과 고성능 FPGA 로직을 목표로 소프트웨어 및 하드웨어 IP를 신속하게 식별하고 재사용 및 통합할 수 있게 된다.

자일링스의 디자인 방법론 마케팅 수석 디렉터인 톰 페이스트(Tom Feist)는 “HLx 에디션은 재사용 가능한 올 프로그래머블 플랫폼의 개발과 프로그래밍을 위한 프레임워크를 제공하고 있다”고 말하며, “모든 비바도 패키지에 고급 툴, IP 및 울트라패스트(UltraFast) 디자인 방법론을 제공해, 자일링스 대부분의 고객들은 가치 차별화에 집중할 수 있게 되었고, 더욱 뛰어난 디자인을 보다 빠르게 얻을 수 있게 되었다”고 덧붙였다.

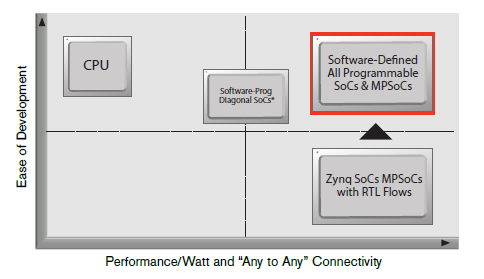

HLx, SDx를 보완하여 플랫폼의 개발 및 배치

HLx는 하드웨어 엔지니어들에게 올 프로그래머블 플랫폼의 개발 및 수정, 프로그래밍에 소요되는 시간을 앞당겨주고, 소프트웨어 및 시스템 엔지니어들에게는 자일링스 SDx 개발 환경(SDSoC™, SDAccel™, SDNet™)을 보완해준다. SDx 제품군의 개발환경은 C 및 C++, OpenCL, 최신 패킷 처리용 P4 언어를 혼합하여 사용함으로써 HLx 생성 플랫폼의 소프트웨어 정의 프로그래밍이 가능하다. HLx와 SDx는 징크 SoC, MPSoC, ASIC 클래스 FPGA 및 3D IC 등이 포함된 차세대 올 프로그래머블 디바이스를 활용하여 더욱 스마트하고 커넥트 및 차별화된 시스템을 개발하는 자일링스의 디자인 이네이블먼트 솔루션의 새로운 세대를 표상하고 있다.

재사용 가능한 플랫폼 개발 및 프로그래밍으로 최고의 생산성

지난 3년 동안 첨단 기술을 보유한 자일링스 고객들은 현재 HLx 에디션에 포함된 C 및 IP 기반 디자인 기술 및 방법론을 개척하여 발전시켰고, 10~15배의 잠재적인 생산성을 입증해왔다. 고객들은 이 생산성을 실현하기 위해 1) C 기반 디자인 및 최적화된 재사용, 2) IP 서브시스템의 재사용, 3) 통합 자동화, 4) 가속 디자인 마무리 등 전체 또는 일부를 채택했다.

디자인 대부분이 디자인 프로세스의 최종 단계에서 소모되는 지금까지의 RTL 기반 디자인과 달리, C 및 IP 기반 디자인은 특히, 디자인 재사용이 탁월해 개발 속도가 빠르고, 보다 나은 세부 아키텍처를 위한 신속한 디자인 탐구가 가능하다. 이로써 오류가 쉽게 발생하는 C의 RTL 수동 변환을 대치하고, C 및 RTL 기반 IP를 통합하는데 드는 시간 및 오류를 덜어주며, 검증 시간을 크게 줄여 준다. 고객들은 High-Level 추상화(abstraction)를 이용해 전반적으로 더 뛰어나거나 동등한 결과 품질(성능, 전력, 활용도)을 빠르게 얻을 수 있다.

이렇게 높은 생산성 흐름을 위해 HLx 에디션은 비바도 HLS, 비바도 IPI, LogicCORE IP 서브시스템, 전체 비바도 구현 툴 수트가 포함되어 있다. 또한 자일링스와 그 얼라이언스 에코시스템은 비디오, 이미지 처리를 위한 OpenCV 및 첨단 운전자 보조 시스템(ADAS)용 머신 학습, 데이터센터 애플리케이션과 같은 시장별 맞춤형 C 라이브러리들을 지속적으로 확대하고 있다. 자일링스의 새로운 LogiCORE IP 서브시스템은 구성 능력이 매우 뛰어난 시장 맞춤형 빌딩 블록으로써, 최대 80개의 개별 IP 코어 및 소프트웨어 드라이버, 디자인 예시, 테스트 벤치 등을 통합하고 있다. 이 새로운 IP 서브시스템을 이더넷, PCIe®, 비디오 처리, 이미지 센서 처리 및 OTN 개발 등에 이용할 수 있다. 또한 IP 서브시스템은 AMBA® AXI 4 인터커넥트 프로토콜, IEEE P1735 암호화, IP-XACT와 같은 산업 표준을 바탕으로 자일링스 및 얼라이언스 회원사 IP와 상호운용성을 보장하고 통합 속도를 앞당긴다.

C 기반 IP 및 사전 패키지 IP 서브시스템은 통합 자동화를 위해 비바도 IP 통합기를 활용하여 빠르게 결합된다. 비바도 IPI의 통합 자동화는 디바이스와 플랫폼을 인식하는 인터랙티브 환경을 통해 핵심 IP 인터페이스의 인텔리전트 자동 연결과 클릭 한 번으로 IP 서브시스템 생성, 실시간 DRC, 인터페이스 변동 전달 능력과 함께 강력한 디버그 능력을 지원한다. 이 플랫폼 인식 인텔리전스는 정확한 주변장치와 드라이버, 메모리 맵으로 징크(Zynq)® SoC 및 MPSoC 프로세서 시스템을 미리 구성하여 타깃 보드를 지원할 수 있다. 디자인 팀은 이제 ARM® 프로세서 시스템과 고성능 FPGA 로직을 목표로 소프트웨어 및 하드웨어 IP를 신속하게 식별하고 재사용 및 통합할 수 있게 된다.

자일링스의 디자인 방법론 마케팅 수석 디렉터인 톰 페이스트(Tom Feist)는 “HLx 에디션은 재사용 가능한 올 프로그래머블 플랫폼의 개발과 프로그래밍을 위한 프레임워크를 제공하고 있다”고 말하며, “모든 비바도 패키지에 고급 툴, IP 및 울트라패스트(UltraFast) 디자인 방법론을 제공해, 자일링스 대부분의 고객들은 가치 차별화에 집중할 수 있게 되었고, 더욱 뛰어난 디자인을 보다 빠르게 얻을 수 있게 되었다”고 덧붙였다.

HLx, SDx를 보완하여 플랫폼의 개발 및 배치

HLx는 하드웨어 엔지니어들에게 올 프로그래머블 플랫폼의 개발 및 수정, 프로그래밍에 소요되는 시간을 앞당겨주고, 소프트웨어 및 시스템 엔지니어들에게는 자일링스 SDx 개발 환경(SDSoC™, SDAccel™, SDNet™)을 보완해준다. SDx 제품군의 개발환경은 C 및 C++, OpenCL, 최신 패킷 처리용 P4 언어를 혼합하여 사용함으로써 HLx 생성 플랫폼의 소프트웨어 정의 프로그래밍이 가능하다. HLx와 SDx는 징크 SoC, MPSoC, ASIC 클래스 FPGA 및 3D IC 등이 포함된 차세대 올 프로그래머블 디바이스를 활용하여 더욱 스마트하고 커넥트 및 차별화된 시스템을 개발하는 자일링스의 디자인 이네이블먼트 솔루션의 새로운 세대를 표상하고 있다.

- 적용분야 :

- Smarter Vision

- 관련제품 :

- Vivado Design Suite