Technical Article

제품 및 Tools

올프로그래머블 시대를 위한 디자인 고려사항

올프로그래머블 시대를 위한 디자인 고려사항

2014-09-01

올프로그래머블 시대를 위한 디자인 고려사항

제공: 톰페이스트(Tom Feist), 자일링스

프로그래머블 디바이스 및 시스템 성능이 갈수록 증가하고, 호평을 얻으면서 다양한 산업 분야의 디자이너를 위한 새로운 차원의 혁신 및 효율이 가능하게 되었다. 하지만 이러한 진보는 새로운 과제를 수반하게 되는데, 새롭게 부상하고 있는 올 프로그래머블(All Programmable) 시대의 완벽한 잠재력을 실현시킬 수 있다면, 이러한 과제들은 해결이 가능하다.

모든 IC 디자이너와 마찬가지로, 프로그래머블 분야의 디자인 팀 또한 새로운 차원의 시스템 통합 및 시스템 성능 증대, BOM 비용절감, 총 시스템 전력소모 절감을 끊임없이 기대하고 있으며, 디자인 생산성을 가속하기 위한 이러한 지속적인 요구의 배경에는 혁신적인 제품을 보다 빨리 마켓에 출시하기 위한 요구가 깔려있다. 칩의 복잡도가 증가함에 따라 새로운 도전과제들이 도출되기 때문에 툴 및 방법론에서 모두 이를 해결할 수 있는 보다 혁신적인 디자인 접근방식이 요구된다.

이는 공급자 및 사용자를 위한 세심한 조정작업이 필요하다. 최신 알고리즘 및 성능, 기능은 툴의 혁신을 가속화하고 있지만, 산업 표준 및 기존 환경 또한 고려해야 한다. 이상적인 것은 고도의 자동화된 푸시버튼플로우를 원하는 디자이너에서 거의 대부분을 수동으로 수행하는 디자이너에 이르기까지 모든 디자이너들이 가장 큰 디바이스라도 이전보다 훨씬 빠르고, 더욱 효율적으로 디자인하는 것은 물론, 기존의 익숙하고 편리한 환경을 유지하면서도 고도로 통합된 환경의 업계 최신 EDA로 작업할 수 있도록 하는 것이다.

이를 위해, 이 글에서는 디자인 팀이 제품의 시장출시 시기(TTM: Time to Market)를 앞당기기 위해 통합을 고려해야 하는 일부 핵심 기능 및 최상의 실행과제들에 대한 필수적인 체크 리스트를 정리했다.

가장 긴급한 디자인 도전과제 해결

대부분의 디자인은 스케쥴이 무엇보다 중요하며, 개발환경은 이를 해결할 수 있어야 한다. 디자이너는 알고리즘 C/C++ 및 RTL(Register-Transfer Level) IP, 혼합 DSP, 임베디드, 커넥티비티, 로직 도메인의 통합을 비롯해, 블록 및 ‘시스템’ 검증, 그리고 내부의 기존 디자인 및 IP 재사용 등 수많은 통합 문제에 직면해 있다. 또한 계층적 칩 플래닝 및 파티셔닝, ‘타이밍’클로저, 느린 ECO 및 디자인 변경에 따른 파급효과 등 여러 구현상의 어려움에도 직면해 있다. 디자이너는 이러한 어려움들을 해결할 수 있고, 차세대 올 프로그래머블 디바이스의 시스템 통합 성능의 혜택을 완벽하게 활용할 수 있도록 해주는 툴이 필요하다.

디자인 방법론으로 예측 가능한 디자인 사이클

디자인 팀은 세계에서 가장 진보된 실리콘 및 세계에서 가장 뛰어난 툴에 액세스할 수는 있지만, 견고한 방법론을 수립하지 못한다면, 적시에 제품을 공급하고, 이를 사업적 성공으로 끌어내기는 어렵다. 뛰어난 디자인 방법론은 디자인 팀이 기한에 맞춰 고품질의 제품을 공급할 수 있도록 디자인 시간을 단축할 뿐만 아니라, 장기적인 사업성공에 핵심인 예측 가능하고 반복적인 방법으로 이를 수행할 수 있도록 해준다. 이는 방법론 또한 반드시 실리콘 및 디자인 툴의 진화에 따른 혜택을 얻을 수 있도록 지속적으로 발전되어야 함을 의미한다.

차세대 혁신을 보다 생산적이고 효율적으로 안착시키기 위해 디자이너들은 산업 전문가들로부터 최상의 실행사례들을 찾아야 하며, 이러한 사례들을 분류하여디자인 팀이 보다 빠르게 성공을 보장할 수 있는 강력한 방법론으로 만들어야 한다. 이러한 최상의 사례들은 보드 플래닝 및 디자인 생성, 검증, 디자인 구현 및 타이밍 클로저, 프로그래밍, 하드웨어 디버깅의 모든 측면들을 커버해야 한다.

예를 들어, 예측 가능한 디자인 사이클을 다루기 위해 자일링스는 무료 방법론 매뉴얼을 발간했다. 비바도(Vivado) 디자인 수트를 위한 울트라패스트(UltraFast) 방법론 가이드(UG949)는 구현 및 최종 디버깅을 위한 방법론 전반 및 보드 선택, 그리고 RTL 디자인 검증을 다루고 있다. 이 문서는 디자인 플로우 전반에 걸쳐 엔지니어를 가이드하고, 최상의 실행사례를 활용할 수 있도록 설계된 포괄적인 체크리스트를 포함하고 있다.

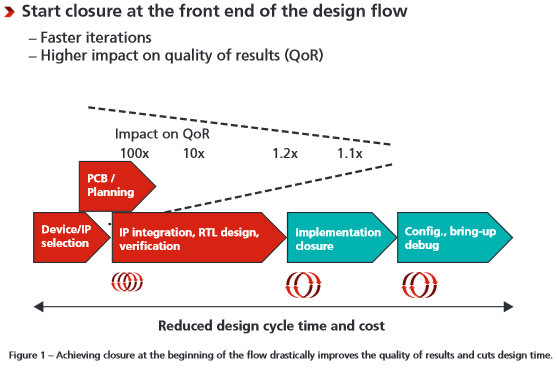

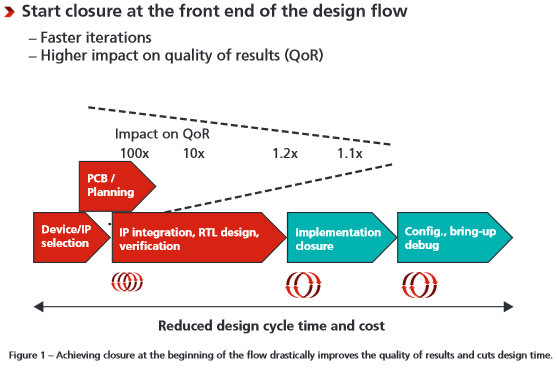

울트라패스트 디자인 방법론의 메인 주제는 품질 결과에 더 큰 영향을 미치는 디자인 플로우 초반에 디자인클로저를 실행하는 것이다.(그림 1 참조) 이러한 방법으로 디자인 팀은 신속하게 디자인의 오류를 제거(Correct-by-Construction)할 수 있다. 만약 정보에 근거한 결정이 플로우 레벨 초기에 이뤄진다면, 구현 단계에서 상당히 긴 사이클을 제거할 수 있다.

그림 1. 플로우 초기에 클로저를 달성하면 품질 결과를 획기적으로 향상시키고,

디자인 시간을 단축할 수 있다.

기존 툴의 경우, 디자이너는 프로세스 후반에완전히 구현된 디자인 상에서만 문제를 발견할 수 있다. 디자인이 예상대로 동작하지 않거나, 타이밍 클로저를 달성할 수 없다면, 오직 하나의 선택은 초기 디자인 단계로 되짚어 돌아가야 하며, 문제의 원인에 대한 단서를 찾기 어렵기 때문에 디자인 팀은 여러 번의 긴 반복적인 과정을 되풀이해야 한다. 솔루션은 디자인 프로세스의 초기 단계에 핵심 디자인 메트릭(타이밍, 전력, 리소스 활용도, 라우팅밀집도 등)으로 가시성을 제공하는 공동의 확장 가능한 데이터 모델을 이용하는 디자인 방법론 및 디자인 툴 수트를 활용하는 것이다. 이 조합을 통해 디자인 팀은 생산성을 가속화하고, 계속해서 디자인플로우를 단축할 수 있으며, 스케쥴을 예측할 수 있어 제품의 마켓출시를 앞당길 수 있다.

비밀 소스: IP가 열쇠

오늘날 거의 모든 IC 및 SoC는 상당한 양의 IP(Intellectual Property)를 통합하고 있다. 목표를 달성하기 위해 디자이너는 산업표준을 채택하고 있고, 특별히 IP 생성 및 통합, 재사용을 용이하게 하는 툴을 제공하는 툴 수트를 통해 혜택을 얻을 수 있다.

IP를 빠르게 구현하고, 디자인 생산성을 향상시키기 위해 디자이너는 핀 레벨이 아닌 인터커넥트 레벨에서 IP를 디자인에 통합할 수 있도록 해주는 툴을 찾아야 한다. 이러한 툴을 통해 디자이너는 드래그&드롭으로 IP를 디자인 안에 통합할 수 있으며, 이 툴은 각각의 인터페이스가 호환 가능한지 미리 체크한다. 이러한 툴의 경우 디자이너가 코어 사이에 하나의 라인을 그리기만 하면, IP를 연결하는 적합한 인터커넥트로직 및 데이터 무버를 자동으로 추론한다.

디자이너가 IP 통합기 툴 기능으로 4개 혹은 5개의 블록을 디자인에 통합한 경우, 디자이너는 이 프로세스의 출력을 얻을 수 있고, 다른 사람이 향후 디자인에 이를 활용할 수 있도록 IP 서브시스템을 생성하는데 병합할 수 있기 때문에 통합 및 검증 시간을 단축할 수 있다.

추상화 및 자동화

추상화 및 자동화는 제품 개발을 가속화하고, 소프트웨어 개발자가 맞춤형 하드웨어 가속기를 사용하고, 시스템 엔지니어가 하드웨어 및 소프트웨어 성능을 최적화할 수 있도록 해준다. 추상화는 FPGA, SoC, 3D IC에 시스템 개발 및 알고리즘을 구축하는 모든 측면을 자동화함으로써 전통적인 RTL 디자인 방법론의 지평을 넓혀준다. 이는 디자인 팀 및 타깃 애플리케이션에 가장 적합한 추상화를 활용함으로써 개발 공정을 가속화하는 포괄적인 솔루션 세트를 제공하기 위해 전략적 비즈니스 파트너와의 강력한 연합이 이뤄지고 있다.

추상적 개념의 자동화는 산업표준 및 오픈 소스 커뮤니티를 채택함으로써 가능하게 되었다. 산업표준 프로그래밍 언어와 이클립스(Eclips)-기반 툴 체인, ARM® AMBA AXI4 인터페이스, 그리고 IP-XACT를 이용한 표준-기반 플러그&플레이 IP와 IEEE1735 암호화를 활용한 툴 수트로작업함으로써,디자인 팀은 올 프로그래머블 FPGA 및 SoC, 3D IC의 자동화를 용이하게 하는 디자인 방법론 및 툴, IP를 쉽게 병합할 수 있다.

C-기반 IP 생성

오늘날 무선 및 의료, 방위, 컨수머 애플리케이션에 사용되고 있는 HLS(High-Level Synthesis) 첨단 알고리즘은 이전보다 훨씬 더 정교해졌다. 이러한 알고리즘의 모델링을 위해, 많은 디자인 팀은 RTL 기반 시뮬레이션에 비해 높은 시뮬레이션 성능을 보여주는 C/C++ 및OpenCL, SystemC에 의존하고 있다. 일부 경우, C 코드는 해당 RTL 보다 1,000배 더 빠르게 구동된다. 문제는 하드웨어를 구현하기 위해 RTL에서 작성된 알고리즘을 재코딩해야 한다는 것인데, 이는 시간 소모가 크고, 오류가 발생하기 쉽다. 디자인 팀은 수작업으로 RTL을 생성할 필요없이 C 사양을프로그래머블 디바이스에 직접 타깃함으로써 프로세스를 가속화는 C-기반 IP 생성 기능을 갖춘 툴 수트를 활용해야 할 것이다.

차세대 프로그래머블 디자인을 위한 툴

EDA 기술은 지난 15년에 걸쳐 상당히 발전해 왔다. 중요한 점은, 오늘날의 엔지니어는 시스템-레벨 통합 및 구현의 생산성 문제를 해결하기 위해 근본적으로 재설계된 차세대 개발 툴을 찾고 있다는 점이다.

최신 EDA 기술과 표준을 이용하고, 가까운 미래에 확장이 가능한 툴 수트를 활용함으로써 디자인 생산성 및 품질 결과를 근본적으로 향상시키는 것은 물론, 디자이너는 보다 뛰어난 시스템을 더 적은 칩으로 보다 빠르게 구현할 수 있게 되었다.

제공: 톰페이스트(Tom Feist), 자일링스

프로그래머블 디바이스 및 시스템 성능이 갈수록 증가하고, 호평을 얻으면서 다양한 산업 분야의 디자이너를 위한 새로운 차원의 혁신 및 효율이 가능하게 되었다. 하지만 이러한 진보는 새로운 과제를 수반하게 되는데, 새롭게 부상하고 있는 올 프로그래머블(All Programmable) 시대의 완벽한 잠재력을 실현시킬 수 있다면, 이러한 과제들은 해결이 가능하다.

모든 IC 디자이너와 마찬가지로, 프로그래머블 분야의 디자인 팀 또한 새로운 차원의 시스템 통합 및 시스템 성능 증대, BOM 비용절감, 총 시스템 전력소모 절감을 끊임없이 기대하고 있으며, 디자인 생산성을 가속하기 위한 이러한 지속적인 요구의 배경에는 혁신적인 제품을 보다 빨리 마켓에 출시하기 위한 요구가 깔려있다. 칩의 복잡도가 증가함에 따라 새로운 도전과제들이 도출되기 때문에 툴 및 방법론에서 모두 이를 해결할 수 있는 보다 혁신적인 디자인 접근방식이 요구된다.

이는 공급자 및 사용자를 위한 세심한 조정작업이 필요하다. 최신 알고리즘 및 성능, 기능은 툴의 혁신을 가속화하고 있지만, 산업 표준 및 기존 환경 또한 고려해야 한다. 이상적인 것은 고도의 자동화된 푸시버튼플로우를 원하는 디자이너에서 거의 대부분을 수동으로 수행하는 디자이너에 이르기까지 모든 디자이너들이 가장 큰 디바이스라도 이전보다 훨씬 빠르고, 더욱 효율적으로 디자인하는 것은 물론, 기존의 익숙하고 편리한 환경을 유지하면서도 고도로 통합된 환경의 업계 최신 EDA로 작업할 수 있도록 하는 것이다.

이를 위해, 이 글에서는 디자인 팀이 제품의 시장출시 시기(TTM: Time to Market)를 앞당기기 위해 통합을 고려해야 하는 일부 핵심 기능 및 최상의 실행과제들에 대한 필수적인 체크 리스트를 정리했다.

가장 긴급한 디자인 도전과제 해결

대부분의 디자인은 스케쥴이 무엇보다 중요하며, 개발환경은 이를 해결할 수 있어야 한다. 디자이너는 알고리즘 C/C++ 및 RTL(Register-Transfer Level) IP, 혼합 DSP, 임베디드, 커넥티비티, 로직 도메인의 통합을 비롯해, 블록 및 ‘시스템’ 검증, 그리고 내부의 기존 디자인 및 IP 재사용 등 수많은 통합 문제에 직면해 있다. 또한 계층적 칩 플래닝 및 파티셔닝, ‘타이밍’클로저, 느린 ECO 및 디자인 변경에 따른 파급효과 등 여러 구현상의 어려움에도 직면해 있다. 디자이너는 이러한 어려움들을 해결할 수 있고, 차세대 올 프로그래머블 디바이스의 시스템 통합 성능의 혜택을 완벽하게 활용할 수 있도록 해주는 툴이 필요하다.

디자인 방법론으로 예측 가능한 디자인 사이클

디자인 팀은 세계에서 가장 진보된 실리콘 및 세계에서 가장 뛰어난 툴에 액세스할 수는 있지만, 견고한 방법론을 수립하지 못한다면, 적시에 제품을 공급하고, 이를 사업적 성공으로 끌어내기는 어렵다. 뛰어난 디자인 방법론은 디자인 팀이 기한에 맞춰 고품질의 제품을 공급할 수 있도록 디자인 시간을 단축할 뿐만 아니라, 장기적인 사업성공에 핵심인 예측 가능하고 반복적인 방법으로 이를 수행할 수 있도록 해준다. 이는 방법론 또한 반드시 실리콘 및 디자인 툴의 진화에 따른 혜택을 얻을 수 있도록 지속적으로 발전되어야 함을 의미한다.

차세대 혁신을 보다 생산적이고 효율적으로 안착시키기 위해 디자이너들은 산업 전문가들로부터 최상의 실행사례들을 찾아야 하며, 이러한 사례들을 분류하여디자인 팀이 보다 빠르게 성공을 보장할 수 있는 강력한 방법론으로 만들어야 한다. 이러한 최상의 사례들은 보드 플래닝 및 디자인 생성, 검증, 디자인 구현 및 타이밍 클로저, 프로그래밍, 하드웨어 디버깅의 모든 측면들을 커버해야 한다.

예를 들어, 예측 가능한 디자인 사이클을 다루기 위해 자일링스는 무료 방법론 매뉴얼을 발간했다. 비바도(Vivado) 디자인 수트를 위한 울트라패스트(UltraFast) 방법론 가이드(UG949)는 구현 및 최종 디버깅을 위한 방법론 전반 및 보드 선택, 그리고 RTL 디자인 검증을 다루고 있다. 이 문서는 디자인 플로우 전반에 걸쳐 엔지니어를 가이드하고, 최상의 실행사례를 활용할 수 있도록 설계된 포괄적인 체크리스트를 포함하고 있다.

울트라패스트 디자인 방법론의 메인 주제는 품질 결과에 더 큰 영향을 미치는 디자인 플로우 초반에 디자인클로저를 실행하는 것이다.(그림 1 참조) 이러한 방법으로 디자인 팀은 신속하게 디자인의 오류를 제거(Correct-by-Construction)할 수 있다. 만약 정보에 근거한 결정이 플로우 레벨 초기에 이뤄진다면, 구현 단계에서 상당히 긴 사이클을 제거할 수 있다.

그림 1. 플로우 초기에 클로저를 달성하면 품질 결과를 획기적으로 향상시키고,

디자인 시간을 단축할 수 있다.

기존 툴의 경우, 디자이너는 프로세스 후반에완전히 구현된 디자인 상에서만 문제를 발견할 수 있다. 디자인이 예상대로 동작하지 않거나, 타이밍 클로저를 달성할 수 없다면, 오직 하나의 선택은 초기 디자인 단계로 되짚어 돌아가야 하며, 문제의 원인에 대한 단서를 찾기 어렵기 때문에 디자인 팀은 여러 번의 긴 반복적인 과정을 되풀이해야 한다. 솔루션은 디자인 프로세스의 초기 단계에 핵심 디자인 메트릭(타이밍, 전력, 리소스 활용도, 라우팅밀집도 등)으로 가시성을 제공하는 공동의 확장 가능한 데이터 모델을 이용하는 디자인 방법론 및 디자인 툴 수트를 활용하는 것이다. 이 조합을 통해 디자인 팀은 생산성을 가속화하고, 계속해서 디자인플로우를 단축할 수 있으며, 스케쥴을 예측할 수 있어 제품의 마켓출시를 앞당길 수 있다.

비밀 소스: IP가 열쇠

오늘날 거의 모든 IC 및 SoC는 상당한 양의 IP(Intellectual Property)를 통합하고 있다. 목표를 달성하기 위해 디자이너는 산업표준을 채택하고 있고, 특별히 IP 생성 및 통합, 재사용을 용이하게 하는 툴을 제공하는 툴 수트를 통해 혜택을 얻을 수 있다.

IP를 빠르게 구현하고, 디자인 생산성을 향상시키기 위해 디자이너는 핀 레벨이 아닌 인터커넥트 레벨에서 IP를 디자인에 통합할 수 있도록 해주는 툴을 찾아야 한다. 이러한 툴을 통해 디자이너는 드래그&드롭으로 IP를 디자인 안에 통합할 수 있으며, 이 툴은 각각의 인터페이스가 호환 가능한지 미리 체크한다. 이러한 툴의 경우 디자이너가 코어 사이에 하나의 라인을 그리기만 하면, IP를 연결하는 적합한 인터커넥트로직 및 데이터 무버를 자동으로 추론한다.

디자이너가 IP 통합기 툴 기능으로 4개 혹은 5개의 블록을 디자인에 통합한 경우, 디자이너는 이 프로세스의 출력을 얻을 수 있고, 다른 사람이 향후 디자인에 이를 활용할 수 있도록 IP 서브시스템을 생성하는데 병합할 수 있기 때문에 통합 및 검증 시간을 단축할 수 있다.

추상화 및 자동화

추상화 및 자동화는 제품 개발을 가속화하고, 소프트웨어 개발자가 맞춤형 하드웨어 가속기를 사용하고, 시스템 엔지니어가 하드웨어 및 소프트웨어 성능을 최적화할 수 있도록 해준다. 추상화는 FPGA, SoC, 3D IC에 시스템 개발 및 알고리즘을 구축하는 모든 측면을 자동화함으로써 전통적인 RTL 디자인 방법론의 지평을 넓혀준다. 이는 디자인 팀 및 타깃 애플리케이션에 가장 적합한 추상화를 활용함으로써 개발 공정을 가속화하는 포괄적인 솔루션 세트를 제공하기 위해 전략적 비즈니스 파트너와의 강력한 연합이 이뤄지고 있다.

추상적 개념의 자동화는 산업표준 및 오픈 소스 커뮤니티를 채택함으로써 가능하게 되었다. 산업표준 프로그래밍 언어와 이클립스(Eclips)-기반 툴 체인, ARM® AMBA AXI4 인터페이스, 그리고 IP-XACT를 이용한 표준-기반 플러그&플레이 IP와 IEEE1735 암호화를 활용한 툴 수트로작업함으로써,디자인 팀은 올 프로그래머블 FPGA 및 SoC, 3D IC의 자동화를 용이하게 하는 디자인 방법론 및 툴, IP를 쉽게 병합할 수 있다.

C-기반 IP 생성

오늘날 무선 및 의료, 방위, 컨수머 애플리케이션에 사용되고 있는 HLS(High-Level Synthesis) 첨단 알고리즘은 이전보다 훨씬 더 정교해졌다. 이러한 알고리즘의 모델링을 위해, 많은 디자인 팀은 RTL 기반 시뮬레이션에 비해 높은 시뮬레이션 성능을 보여주는 C/C++ 및OpenCL, SystemC에 의존하고 있다. 일부 경우, C 코드는 해당 RTL 보다 1,000배 더 빠르게 구동된다. 문제는 하드웨어를 구현하기 위해 RTL에서 작성된 알고리즘을 재코딩해야 한다는 것인데, 이는 시간 소모가 크고, 오류가 발생하기 쉽다. 디자인 팀은 수작업으로 RTL을 생성할 필요없이 C 사양을프로그래머블 디바이스에 직접 타깃함으로써 프로세스를 가속화는 C-기반 IP 생성 기능을 갖춘 툴 수트를 활용해야 할 것이다.

차세대 프로그래머블 디자인을 위한 툴

EDA 기술은 지난 15년에 걸쳐 상당히 발전해 왔다. 중요한 점은, 오늘날의 엔지니어는 시스템-레벨 통합 및 구현의 생산성 문제를 해결하기 위해 근본적으로 재설계된 차세대 개발 툴을 찾고 있다는 점이다.

최신 EDA 기술과 표준을 이용하고, 가까운 미래에 확장이 가능한 툴 수트를 활용함으로써 디자인 생산성 및 품질 결과를 근본적으로 향상시키는 것은 물론, 디자이너는 보다 뛰어난 시스템을 더 적은 칩으로 보다 빠르게 구현할 수 있게 되었다.

- 태그 :

- 알고리즘 C/C++ 및 RTL(Register-Transfer Level) IP, 혼합 DSP, 임베디드, 커넥티비티, 로직 도메인

- 적용분야 :

- Automotive, Aerospace and Defense, Broadcast, Consumer Electronics, Data Center, High Performance Computing, Industrial, Medical, Security, Smarter Networks, Smarter Vision, Wired Communications, Wireless Communications

- 관련제품 :

- UltraScale, Vivado Design Suite